- 您现在的位置:买卖IC网 > Sheet目录1220 > IP-SDRAM/DDR2 (Altera)IP DDR2 SDRAM CONTROLLER

�� �

�

�

�Chapter� 3:� Functional� Description�

�3–3�

�OpenCore� Plus� Time-Out� Behavior�

�IP� Toolbench� generates� a� clear-text� VHDL� or� Verilog� HDL� datapath,� which� matches�

�your� custom� variation.� If� you� are� designing� your� own� controller,� Altera� recommends�

�that� you� use� this� module� as� your� datapath.� IP� Toolbench� generates� placement�

�constraints� in� the� form� of� reusable� scripts� for� all� the� critical� registers� in� Cyclone� series�

�and� for� the� resynchronization� registers� in� Stratix� series.� Altera� recommends� that� you�

�also� use� these� scripts� so� that� your� own� DDR� and� DDR2� SDRAM� designs� have�

�consistent� placement� and� the� timing� analysis� script� results� apply� to� your� design.�

�The� datapath� instantiates� one� or� more� data� strobe� (DQS)� groups.� The� DQS� group�

�module's� control_wdata� and� control_rdata� are� fixed� at� 16� bits� and� data� (DQ)� is�

�fixed� at� 8� bits.� To� build� datapaths� larger� than� 16� bits,� the� datapath� instantiates�

�multiple� DQS� group� modules� to� increase� the� data� bus� width� in� increments� of� 16� bits�

�(8� bits� for� the� DDR� and� DDR2� SDRAM� side).�

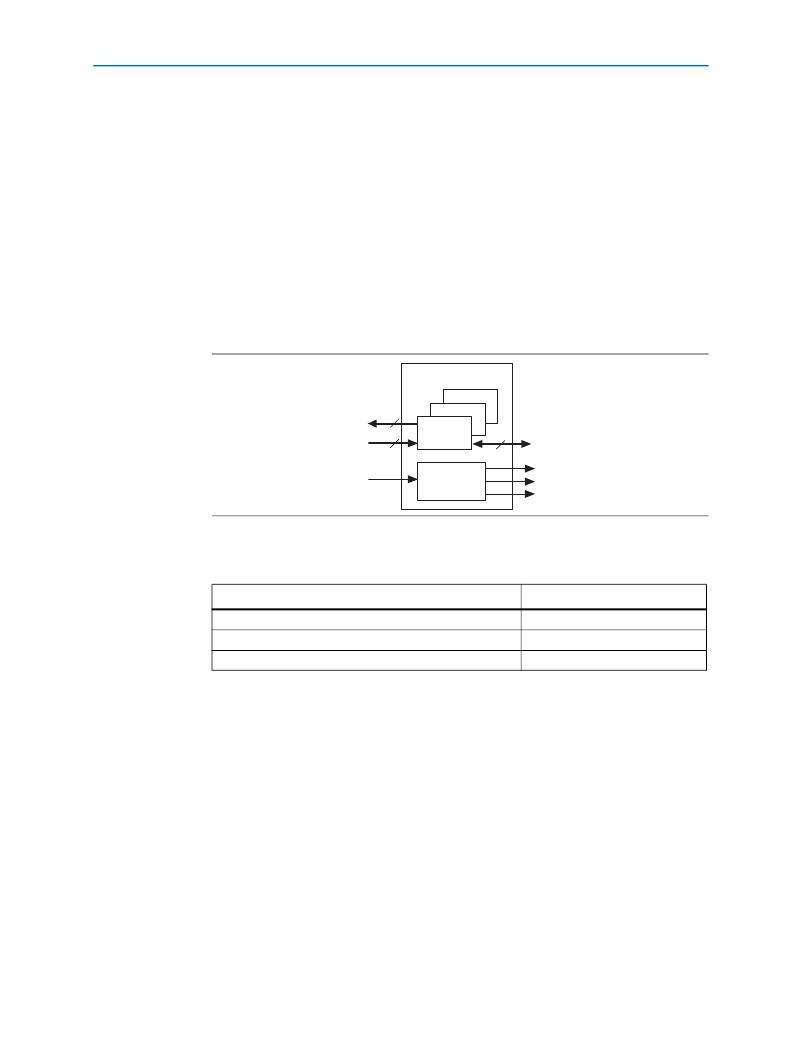

��Figure� 3–2.� Datapath�

�Data� Path� Module�

�16�

�control_rdata�

�control_wdata�

�clk�

�16�

�DQS�

�Groups�

�Clock� Output�

�Generator�

�8�

�dq�

�clk_to_sdram�

�clk_to_sdram_n�

�fedback_clock_out�

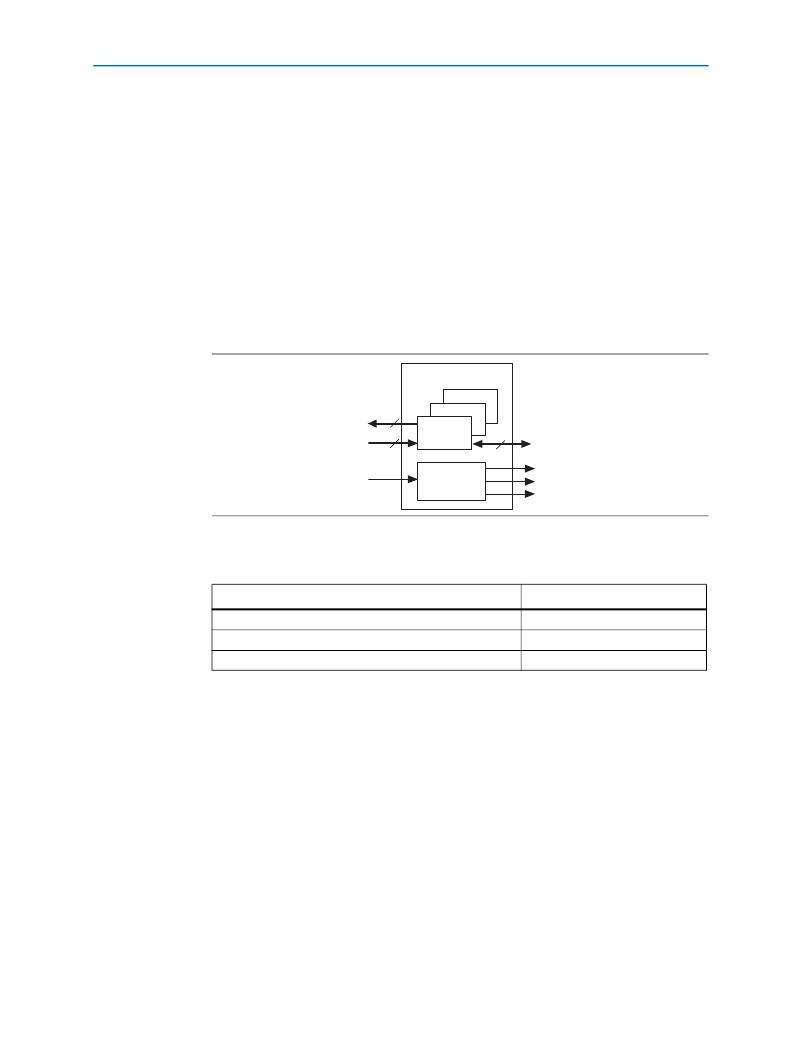

��Table� 3–2.� Datapath� Files�

�Filename�

�<variation� name>� _auk_ddr_datapath.v� or� .vhd�

�<variation� name>� _auk_ddr_clk_gen.v� or� .vhd�

�<variation� name>� _auk_ddr_dqs_group.v� or� .vhd�

�Description�

�Datapath.�

�Clock� output� generator.�

�DQS� groups.�

�f�

��OpenCore� Plus� Time-Out� Behavior�

�OpenCore� Plus� hardware� evaluation� can� support� the� following� two� modes� of�

�operation:�

�■�

�■�

�Untethered—the� design� runs� for� a� limited� time�

�Tethered—requires� a� connection� between� your� board� and� the� host� computer.� If�

�tethered� mode� is� supported� by� all� megafunctions� in� a� design,� the� device� can�

�operate� for� a� longer� time� or� indefinitely�

�?� March� 2009�

�Altera� Corporation�

��发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IP-SLITE2

IP SERIALLITE II

IP-SRAM/QDRII

IP QDRII SRAM CONTROLLER

IP-VITERBI/SS

IP VITERBI LOW-SPEED

IP4220CZ6,125

IC USB DUAL ESD PROTECT 6TSOP

IPA-66-1-600-10.0-A-01-T

CIRC BRKR 10A 2POLE SCREW TERM

IPR-CSC

IP COLOR SPACE CONVERTER RENEW

IPR-ED8B10B

IP 8B10B ENCODER/DECODER RENEW

IPS-VIDEO

IP VIDEO/IMAGE PROCESSING SUITE

相关代理商/技术参数

IP-SDRAM/DDR3

功能描述:开发软件 DDR3 SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IP-SDRAM/HPDDR

功能描述:开发软件 DDR SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IP-SDRAM/HPDDR2

功能描述:开发软件 DDR2 SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IP-SDRAM/LPDDR2

功能描述:开发软件 DDR2 SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPSE.4.33SM600

制造商:Banner Engineering 功能描述:FIBER IPSE.4.33SM600 GLASS FIBER (MIN ORDER 50)

IPSE.4.62SM600

制造商:Banner Engineering 功能描述:FIBER IPSE.4.62SM600 GLASS FIBER (MIN ORDER 50)

IPS-EMBEDDED

功能描述:开发软件 Embedded IP Suite MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPS-EVAL-EH-01

功能描述:ENERGY HARVESTING BOARD RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:THINERGY® 标准包装:1 系列:- 主要目的:数字电位器 嵌入式:- 已用 IC / 零件:AD5258 主要属性:- 次要属性:- 已供物品:板 相关产品:AD5258BRMZ1-ND - IC POT DGTL I2C1K 64P 10MSOPAD5258BRMZ10-ND - IC POT DGTL I2C 10K 64P 10MSOPAD5258BRMZ100-ND - IC POT DGTL I2C 100K 64P 10MSOPAD5258BRMZ50-ND - IC POT DGTL I2C 50K 64P 10MSOPAD5258BRMZ1-R7-ND - IC POT DGTL I2C 1K 64P 10MSOPAD5258BRMZ10-R7-ND - IC POT DGTL I2C 10K 64P 10MSOPAD5258BRMZ50-R7-ND - IC POT DGTL I2C 50K 64P 10MSOPAD5258BRMZ100-R7-ND - IC POT DGTL I2C 100K 64P 10MSOP